7.1 - Los flip-flops TTL

La familia de circuitos integrados digitales TTL, y sus varias subfamilias, tienen una gran cantidad de flip-flops que se pueden utilizar en una multitud de aplicaciones prácticas.

La diferencia de cada tipo de circuito integrado no es sólo el tipo de flip-flop que contiene, así como sus recursos y su cantidad.

También debemos tener en cuenta que un factor importante en la elección de un flip-flop para una aplicación determinada es su velocidad. Para las distintas familias TTL podemos especificar las velocidades medias máximas de sus flip-flop de la siguiente manera:

Standard (74) - 35 MHz

Low Power (74L) - 3 MHz

Low Power Shottky (74LS) - 45 MHz

High Speed (74H) - 50 MHz

Shottky (74S) - 125 MHz

Recordamos a los lectores que, para poder utilizar bien los flip-flops TTL, es necesario observar algunas precauciones, como mantener siempre las entradas CLEAR y PRESET a niveles definidos. Dejar estas entradas abiertas puede producirse inestabilidades de funcionamiento.

El nivel en el que deben ser dejados, o sea, su conexión en Vcc o 0 V depende de la aplicación.

También es importante notar que, a medida que las velocidades de operación se hacen más grandes, más crítica se convierte en el proyecto de las placas de circuito impreso en las que se utilizan estos circuitos integrados.

Técnicas especiales de desacoplamiento de la alimentación, el posicionamiento de los senderos debe conocerse a todos los que pretendan trabajar con tales circuitos integrados.

Analicemos las características de algunos de los flip-flops TTL más utilizados en los proyectos prácticos:

a) 7473 – Doble flip-flop J-K con Clear

En un solo cubierta de 14 pinos Dual in Line tenemos 2 flip-flops del tipo J-K con la entrada CLEAR. El pinaje de este circuito integrado se muestra en la figura 169. También hay versiones del mismo circuito integrado para montaje en superficie.

Los flip-flops de este CI son sensibles al nivel del clock (Level Triggered), con la entrada de CLEAR asincrónica. El funcionamiento de los flip-flops de este circuito integrado se puede entender mejor por la tabla-verdad dada en la figura 170.

En esta tabla, el símbolo que tiene la forma de un pulso de señal representa un pulso de clock positivo aplicado a la entrada correspondiente. Este tipo de representación es muy común en muchos manuales técnicos. El lector debe familiarizarse con su significado.

Tenga en cuenta que cuando J y K están puestos a tierra el clock no tiene ningún efecto en el circuito. En el funcionamiento normal, la entrada transparente debe mantenerse en el nivel alto. Si la entrada Clear es puesta a tierra el flip-flop resetea.

La frecuencia máxima de funcionamiento de estos flip-flop, para la serie normal, es de 20 MHz con un consumo por circuito integrado del orden de 20 mA.

b) 7474- Doble flip-flop tipo D con Preset y Clear

Los flip-flops contenidos en la cubierta DIL de 14 pinos de este circuito integrado desencadenan la transición de señal activada por el borde positivo. El pinaje de este circuito integrado se muestra en la figura 171.

También podemos encontrar versiones para montaje en superficie, con el mismo pinaje.

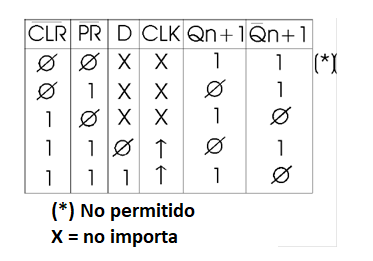

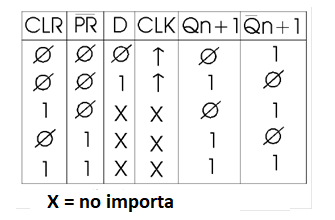

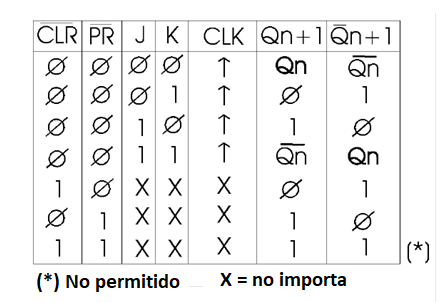

La tabla verdad que muestra el funcionamiento de los flip-flops de este circuito integrado se da en la figura 172.

Por la tabla, vemos que la condición en la que las entradas Clear y Preset son simultáneamente activas no debe ser utilizada, porque tendremos una condición no permitida para los flip-flops.

Este es uno de los casos que citamos, en los que hay combinaciones de entrada prohibida y por lo tanto debe evitarse.

La frecuencia de funcionamiento máxima de este circuito integrado, en la versión standard, es de 25 MHz y el consumo es del orden de 17 mA.

Les recordamos que hay otras versiones que son más rápidas, que han sido estudiadas en lecciones anteriores. También es importante tener en cuenta que todos los componentes de esta línea se pueden encontrar en cubiertas SMD.

En la figura 173 el 74LTX74MTC de Fairchild en la cubierta de SMD.

c) 7475 - Cuatro latches tipo D

Los latches biestables, como ya hemos explicado, son como llaves que almacenan una información digital presente en su entrada. La aplicación más común es precisamente como memoria lo que significa que cada circuito integrado 7475 puede almacenar 4 bits de información.

El pinaje de este circuito integrado se muestra en la figura 174.

Cuando el circuito es habilitado, lo que se consigue tomando la línea "ENABLE" al nivel alto, las salidas Q y /Q siguen la entrada D.

Los latches contenidos en este circuito integrado son del tipo "transparente", lo que significa que si las entradas son modificadas, las salidas también cambian en el mismo instante.

Cuando la entrada "ENABLE" se toma a un nivel bajo, las salidas no responden a las señales de entrada D.

Vea que LATCH almacena la información que estaba en la entrada D inmediatamente antes de que ocurriera una transición de alto nivel al nivel bajo de la línea de habilitación (nivel 1 a nivel 0).

El funcionamiento de cada flip-flop 7475 se puede colocar en la tabla verdad de la figura 175.

Este circuito integrado no es adecuado para aplicaciones donde se desean cambios de estado para cada pulso de clock. Decimos que este circuito no puede ser utilizado como un registrador de desplazamiento (shift-register), una función que se estudiará en las próximas lecciones.

El tiempo de propagación de la señal es del orden de 24 ns y el consumo típico por circuito integrado es de 32 mA, para los componentes de la serie normal o standard.

d) 7476 – Dos flip-flops J-K con Preset y Clear

Los dos flip-flops de este circuito integrado tienen funcionamiento independiente y disparan con el cambio del nivel de la señal del clock (level triggered).

La cubierta es DIL de 16 pinos como se muestra en la figura 176, pero hay versiones con cubiertas de montaje en superficie (SMD).

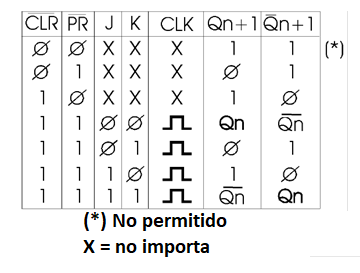

La operación de cada uno de los flip-flops se puede analizar mejor a través de la tabla de la verdad que se muestra en la figura 177.

Tenga en cuenta el símbolo adoptado para representar un pulso de clock.

De la misma manera que en los otros circuitos integrados de esta serie, las entradas CLEAR y PRESET deben mantenerse a niveles lógicos definidos para que no se produzca el funcionamiento errático del circuito.

Las condiciones en las que tenemos ambos resultados en el nivel 1 son condiciones prohibidas, como ya hemos visto, deben evitarse en el uso del componente.

También notamos de la tabla verdadera que no puede activar las dos entradas del CLOCK Y CLEAR al mismo tiempo, pues esto conduciría los flip-flops a una condición no permitida. Esta es otra condición prohibida para el componente indicado.

Un punto interesante, que debe observarse en este circuito integrado, es el pinaje diferente, ya que normalmente en los circuitos de esta serie la alimentación positiva es siempre en los pinos 14 o 16 y la negativa en el pino 7 o 8 cuando las cubiertas son 14 o 16 pinos.

De hecho, el proyectista debe ser consciente de este hecho, porque no es sólo ese componente que no sigue esta regla. Otros componentes pueden tener alimentaciones hechas por diferentes pinos.

La frecuencia máxima de funcionamiento de estos flip-flops para la serie normal es 20 MHz y el consumo es de 20 mA.

e) 74174 – Seis flip-flops tipo D con Clear

Este circuito integrado contiene seis flip-flops de tipo D que se activan en la transición positiva de la señal del clock. La entrada de CLEAR es común a todos los flip-flops. La cubierta es de 16 pinos con la identificación hecha según muestra la figura 178.

La tabla verdad que describe el funcionamiento de cada flip-flop de este circuito integrado se muestra en la figura 179.

Tenga en cuenta que en estos flip-flops tenemos acceso a sólo una de las salidas, lo que significa que las salidas complementares realmente no pueden ser utilizadas.

De hecho, la mayoría de las aplicaciones en las que se usan flip-flops sólo toman una de las salidas. Por lo tanto, no hay necesidad de tener acceso a la salida complementar en estos casos. Este acceso, siendo eliminado, puede ayudar no sólo en la integración de mayor número de flip-flops en la misma cubierta, sino también en el uso de menos pinos.

La frecuencia máxima de cada flip-flop en la serie standard (común) es de 35 MHz con un consumo típico de 45 mA por circuito integrado.

f) 74273- Ocho flip-flops tipo D con Clear

Este circuito es similar al anterior, con la diferencia de que hay ocho en lugar de seis flip-flops tipo D. como cada flip-flop puede funcionar con un bit, este ajuste se convierte en ideal para aplicaciones en computadoras ya que puede operar con 8 bits que corresponden a un Byte.

El pinaje del circuito integrado 74273 se muestra en la figura 180.

La tabla verdadera para cada flip-flop es la misma del circuito integrado anterior y que fue mostrada en la figura 180.

La frecuencia de funcionamiento máxima para los circuitos integrados de este tipo de serie normal es de 30 MHz, con un consumo de 62 mA para cada uno.

Vea que la cubierta utilizada es Dual In Line (DIL) de 20 pinos y que la entrada CLEAR es común a todos integrados. En otras palabras, un pulso en la entrada de CLEAR, cera todos los flip-flops de este circuito integrados al mismo tiempo.

También observamos que no hay acceso a los resultados complementarios de cada flip-flop, y que las versiones se pueden obtener para SMD.

g) 74LS373 – Latch octal transparente tipo D

El tipo LS (Low Power Schottky) es importante en determinadas aplicaciones, ya que es un circuito compatible con los puertas paralelos de ordenadores, y también con microprocesadores utilizados en controles y automatización industrial. Esto significa que puede ser excitado por los niveles lógicos existentes en un PC o un microprocesador.

Como cada circuito integrado 74LS373 contiene 8 lactchs con salidas tri-state, se puede utilizar para trabajar con un byte completo, sin problemas. Cada flip-flop almacena un bit.

El Pinaje de este circuito integrado se muestra en la figura 181.

Cuando la entrada/OE está en el nivel alto (1) las salidas de todos los flip-flops van al estado de alta impedancia. Esto significa que estas salidas pueden conectarse a un bus común a otros circuitos integrados sin el problema de los conflictos que pueden cargar los circuitos causando problemas de funcionamiento, como ya hemos estudiado en las lecciones iníciales de este curso.

La precaución principal que debe tomarse cuando estas salidas están conectadas a un bus y que no sean inadvertidamente activadas cuando el bus este transmitiendo señales porque pueden producirse conflictos de nivel lógico.

Cuando se activa la entrada /OE, lo que se hace al llevarlo al nivel bajo (0), el estado de las salidas dependerá de la entrada EL. Si EL se coloca en el nivel alto (1), el latch estará abierto y éste se encuentra en el estado "transparente". Lo que esté en la entrada D pasará por el circuito y aparecerá en la salida Q.

Si EL está a bajo nivel (0) la salida Q ya no responde a lo que ocurre en las entradas d. en estas condiciones decimos que el latch está cerrado y la salida Q será el contenido de las entradas D que se almacenó inmediatamente antes de la transición de las entradas EL del nivel alto al nivel bajo.

En otras palabras, podemos decir que los flip-flops son gatillados en la transición negativa de la entrada. El almacenamiento de la información que se les aplica en la entrada.

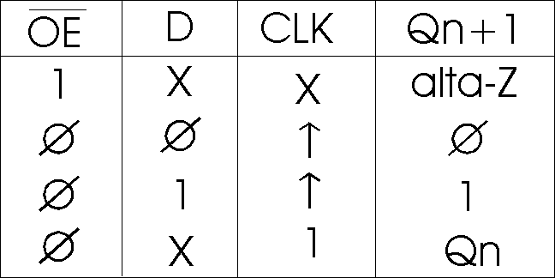

La tabla verdad en la figura 182 muestra lo que sucede en cada flip-flop de este circuito integrado.

Observe la condición de alta impedancia obtenida con /OE en el nivel alto.

La frecuencia máxima de funcionamiento de los latchs de este circuito integrado es de 50 MHz con un consumo de 24 mA.

h) 74LS374 – Ocho flip-flops tipo D con salidas Tri-State

El circuito integrado TTL 74LS374, presentado en un cubierta DIL de 20 pinos, contiene 8 flip-flop de tipo D que se activan en la transición positiva de la señal del clock. Las salidas son Tri-State y la patilla se muestra en la figura 183.

Cuando la entrada /OE está en el nivel alto, las salidas de todos los flip-flops van al estado de alta impedancia.

Vea que en este circuito integrado. Tampoco tenemos acceso a los resultados complementarios de cada flop-flop.

La tabla verdad que describe el funcionamiento de cada flip-flop se muestra en la figura 184.

La frecuencia de funcionamiento máxima de este circuito integrado es de 50 MHz, con un consumo típico de 27 mA.

Tenga en cuenta que tenemos un clock común para todos los flip-flops.

7.2- Los flip-flops CMOS

La familia de circuitos integrados CMOS también tiene una gran cantidad de circuitos integrados que contienen flip-flops.

Aunque los principios de funcionamiento de estos flip-flop son los mismos, las características eléctricas son diferentes. Así, la tensión de la alimentación, la sensibilidad del ruido, la velocidad, el etc. son diferentes, que se deben tener en cuenta en cualquier proyecto.

Una recomendación importante con respecto al uso de estos flip-flop, así como las otras funciones del CMOS, es que las entradas no utilizadas, debido a su alta sensibilidad de la impedancia nunca se deben mantener abiertas cuando hay posibilidad de capturar ruidos.

En los flip-flops CMOS, a diferencia de los TTL, las entradas asincrónicas se activan en el nivel alto, lo que significa que deben mantenerse a un nivel bajo para un funcionamiento normal.

Esto significa que en aplicaciones prácticas los pinos correspondientes deben estar puestos a tierra.

a) 4013 - Dos flip-flops tipo D con Preset y Clear

El circuito 4013 es uno de los más populares en la serie CMOS, siendo empleado en una multitud de proyectos prácticos.

Los dos flip-flops contenidos en este circuito integrado se activan en la transición positiva de la señal del clock. La cubierta es el DIL de 14 pinos que se muestra en la figura 185.

La tabla verdad para este circuito integrado se muestra en la figura 186.

Por la tabla verdad, vemos que las entradas CLEAR y PRESET están activas en el nivel alto, pero sólo una de ellas puede estar en esta condición a la vez. Si las dos entradas PRESET y CLEAR se colocan en el nivel alto al mismo tiempo, el flip-flop pasa a una condición que no está permitida.

La información presente en la entrada D se transfiere a la salida cuando las entradas asíncronas PRESET y CLEAR están inactivas.

Es importante tener en cuenta que la velocidad de funcionamiento de los circuitos CMOS depende de la tensión de alimentación, como ya hemos estudiado en las lecciones anteriores.

En los manuales de circuitos integrados CMOS los lectores pueden encontrar tablas que dan los distintos tiempos de propagación de señales y frecuencias de operación dependiendo de esta tensión de alimentación.

La siguiente tabla ofrece las principales características de este componente:

b) 4027 – Doble Flip-Flop J-K con Preset y Clear

En este circuito integrado encontramos dos flip-flops tipo J-K con entradas de PRESET y CLEAR. La cubierta es DIL de 16 pinos, que se muestra en la figura 187.

Las entradas PRESET y CLEAR son independientes para cada flip-flop. La tabla verdad para cada flip-flop se muestra en la figura 188.

Tenga en cuenta que tenemos acceso a las salidas normales como complementar de cada uno de los flip-flops, y que las salidas CLEAR y PRESET están activas en el nivel alto. Sin embargo, al igual que en los otros flip-flops, estas salidas no se pueden activar al mismo tiempo, ya que tomarían los flip-flops a una condición no permitida.

La tabla que se indica a continuación proporciona las principales características eléctricas del 4027.

c) 4043- Cuatro Flip-Flops R-S (Lógica NOR)

El circuito integrado 4043 contiene cuatro flip-flops independientes de R-S con salidas Tri-State. La cubierta DIL de 16 pinos se muestra en la figura 189.

En cada uno de los flip-flop las entradas SET y RESET normalmente pueden permanecer en el nivel bajo. Si la entrada SET se coloca en nivel alto, la salida permanecerá en el nivel alto. Si la entrada de restablecimiento se lleva al nivel alto, la salida permanece a un nivel bajo. Las dos salidas no se pueden tomar al mismo tiempo en el nivel alto, ya que esto representa un estado no permitido.

Le recordamos que los estados no permitidos pueden ser peligrosos para la integridad del componente que conduce a una mayor disipación.

Las salidas van al estado de alta impedancia cuando las entradas EN (habilitación o ENABLE) se toman a un nivel bajo. Cuando el nivel de la entrada EN es alto, las salidas se conectan a los flip-flop transfiriendo sus estados a los circuitos externos.

Dado que estos circuitos no utilizan clock, no se deben conectar en cascada para formar contadores o shift-registers.

La tabla dada en la figura 190 proporciona las características eléctricas principales del 4043.

Observe que este dispositivo tiene capacidades diferentes de suministro y drenaje de alimentación en sus salidas

d) 40174- Seis flip-flops tipo D

El circuito integrado CMOS 40174 contiene seis flip-flops tipo D, disparados por la transición positiva de la señal del clock. Sólo uno de los resultados de cada flip-flop es accesible externamente y el claro es común a todos ellos.

La cubierta es DIL de 16 pinos con el pinaje que se muestra en la figura 191.

Todos los flip-flops son controlados por una entrada común del clock.

La tabla verdad para cada flip-flop de este circuito integrado se muestra en la figura 192.

En la tabla de la figura 193 le damos las principales características eléctricas de este circuito integrado.

Es interesante notar que este dispositivo es equivalente a TTL 74174.

e) 40175 – Cuatro flip-flops tipo D

Es un circuito integrado que contiene cuatro flip-flops similares a los anteriores, con la diferencia de que las dos salidas (normales y complementar) de cada flip-flop pueden ser accedidas. La cubierta de este circuito integrado se muestra en la figura 194.

La tabla verdad para cada circuito integrado es la misma que 40174.

Las características eléctricas del 40175 son las mismas que 40174.

Este circuito integrado es equivalente en función al TTL 74192.

7.3 – Funciones de lógica TTL

Podemos contar con una buena cantidad de circuitos integrados que contengan las principales funciones lógicas en la tecnología TTL. Seguimos algunos de los más importantes, ya que para obtener información sobre todo lo que están disponibles, será interesante para el lector a depender de un manual TTL o utilizar los motores de búsqueda de Internet.

a) 7400– Cuatro Puertas NAND de dos entradas

En una cubierta DIL de 14 pinos tenemos cuatro puertas NAND de dos entradas de operaciones independientes. El pino de este circuito integrado se muestra en la figura 195.

El consumo medio por circuito integrado está en el orden de 12 mA.

Recordamos que el pino para los equivalentes de las subfamilias es la misma, y que también queda para las cubiertas SMD.

b) 7402- Cuatro puertas NOR de dos entradas

Este circuito integrado en cubierta DIL de 14 pinos tiene pinaje que se muestra en la figura 196, y cada unidad requiere una corriente de 12 mA.

Las cuatro puertas contenidos en este circuito integrado se pueden utilizar de forma independiente.

c) 7404-Seis inversores (Hex Inverter)

Los seis inversores de este circuito integrado se pueden utilizar de forma independiente. El pinaje se muestra en la figura 197.

Las salidas de los inversores 7404 pueden drenar hasta 30 mA a nivel bajo y con una alimentación de hasta 30 V. Sin embargo, recordamos que incluso con el Circuito de salida siendo alimentado por 30 V, el circuito integrado debe mantener su alimentación a 5 V.

d) 7408- Cuatro puertas AND de dos entradas

Este circuito integrado tiene el pinaje que se muestra en la figura 198 y cada unidad requiere una corriente de 16 mA.

Los puertas contenidos en 7408 se pueden utilizar de forma independiente.

e) 7410– Tres puertas NAND de tres entradas

Cada uno de las tres puertas NAND de este circuito integrado se puede utilizar de forma independiente. La corriente requerida por el circuito es de 6 mA. La figura 199 muestra su pinaje.

Esta pinaje también es válida para los equivalentes de las otras subfamilias.

f) 7420– Dos puertas NAND de cuatro entradas

Este circuito integrado contiene dos puertas NAND de cuatro entradas que se pueden utilizar de forma independiente. El Pino se muestra en la figura 200.

El consumo por unidad es de aproximadamente 4 mA.

El pinaje para la misma función de las subfamilias es la misma.

También observamos que, cuando una de las entradas no se utiliza, ella

puede ser colocada en el nivel apropiado para ser desactivada.

g) 7432- Cuatro puertas OR de dos entradas

Los puertas OR del circuito integrado TTL 7432 se pueden utilizar independientemente y la corriente total requerida es del orden de 19 mA. El pinaje se muestra en la figura 201.

El Pinaje para los componentes de las subfamilias se mantiene, así como de las versiones SMD.

h) 7486- Cuatro Puertas OR-Exclusivo

Las puertas OU-exclusivo o Exclusive OR de este circuito integrado se pueden utilizar independientemente. El consumo es de 30 mA y el pinaje se muestra en la figura 202.

Para los mismos componentes de las subfamilias el pinaje se mantiene.

7.4 – Funciones lógicas CMOS

También podemos contar con una buena cantidad de circuitos integrados CMOS que contienen funciones lógicas. Por supuesto, no tenemos espacio para poner todas estas funciones en esta lección, siendo recomendado al lector para consultar un manual CMOS, visitar algún sitio web del fabricante en Internet o la página web del autor de este libro.

Daremos a continuación informaciones básicas acerca de algunos de los más comúnmente utilizadas.

Observamos que las informaciones sobre los CIs que estamos poniendo en este curso es lo suficientemente básica para la realización de un proyecto cuyas características no sean críticas. Para los casos en que las velocidades, los tiempos y las corrientes sean críticos, la información adicional dada por los gráficos característicos se debe obtener de los manuales del fabricante.

a) 4001- Cuatro Puertas NOR de dos entradas

Este circuito integrado contiene cuatro puertas OR en una cubierta DIL de 14 pinos con la Pino que se muestra en la figura 203.

En la tabla de la figura 204 tenemos las principales características eléctricas de este circuito integrado.

Si las entradas de las puertas de este IC están interconectadas obtenemos la función inversa.

El 4002, de la misma serie, consiste en puertas NOR de 4 entradas.

b) 4011– Cuatro puertas NAND de dos entradas

En un cubierta DIL de 14 pinos encontramos cuatro puertas NOR de dos entradas de funcionamiento independientes. La cubierta con la identificación de los pinos se muestra en la figura 205.

En la tabla de la figura 206, tenemos las características eléctricas de este circuito integrado.

Si las entradas de cada uno de las puertas fueren interconectadas, obtenemos inversores lógicos.

c) 4012– Dos puertas NAND de cuatro entradas

Las cuatro puertas de dos entradas de este circuito integrado se pueden utilizar independientemente. La identificación de los terminales de este circuito integrado se muestra en la figura 207.

En la tabla de la figura 208 tenemos las características eléctricas del 4012.

Para obtener una función NAND de 3 entradas, desde los puertas existentes en este circuito integrado, simplemente conecte la puerta no utilizado al nivel alto.

d) 4023 - Tres puertas NAND de 3 tres entradas

Las tres puertas NAND de este circuito integrado se pueden utilizar de forma independiente. El pinaje se muestra en la figura 209.

La tabla dada en la figura 210 proporciona las principales características eléctricas de este circuito integrado.

Para utilizar cualquiera de las puertas como una función NAND de dos entradas, simplemente conecte el remanente al nivel lógico "1". Para usarlo como inversor, simplemente conecte las tres entradas de un puerto.

e) 4025- Tres puertas NOR de tres entradas

Encontramos en este circuito integrado tres funciones NOR que se pueden utilizar de forma independiente. El pinaje se muestra en la figura 211.

En la tabla dada en la figura 212 tenemos las principales características eléctricas de este circuito integrado.

Cada puerto se puede utilizar como la función E (AND) de dos entradas, si el puerto restante fuera conectado a tierra.

7.5- La Función Tri-State Expansível del 4048

El circuito integrado 4048 tiene características muy interesantes para los proyectos CMOS que implican funciones lógicas.

A medida que estudiamos, utilizando combinaciones apropiadas de funciones sencillas podemos conseguir cualquier otra función más compleja. Esto es exactamente lo que hace el 4048 que tiene los pinos mostrados en la figura 213.

Este circuito tiene 8 entradas de señal y una salida de señal más tres entradas de "programación". Dependiendo de los niveles lógicos aplicados a las entradas de programación, el circuito se compone como una función diferente.

Así, puede convertirse en funciones NOR, OR, NAND o AND con 8 entradas o incluso combinadas, realizando al mismo tiempo funciones de puertas OR y AND, cada 1 de 4 entradas además de otras que se muestran en detalle en la figura 214.

Así, por ejemplo, si ponemos las tres entradas de programación en el nivel alto (ka, Kb y Kc = 111) el circuito se comporta como dos puertas AND de cuatro entradas, conectados a un puerto OR de dos entradas.

Vea entonces que esta interesante función puede servir como "comodín" en muchos proyectos, pues puede asumir la operación de varias combinaciones de otros circuitos integrados del CMOS.

Internamente el 4048 es bastante complejo, conteniendo 32 funciones independientes que son programadas por los niveles lógicos aplicados a las entradas correspondientes.

Las características eléctricas del 4048 son dadas en la tabla de la figura 215:

Dos hechos relevantes atraen la atención de quienes usarán esta función en algún proyecto.

El primero de ellos es el alta capacidad de suministro o drenaje de corriente de las salidas, que es mucho mayor que los demás tipos de esa serie.

El segundo hecho es la baja velocidad de operación, con un tiempo relativamente largo que el circuito necesita para procesar la señal, dada por el tiempo de propagación.

Sumário

Curso de Electrónica - Electrónica Digital (CUR5000)

Curso de Electrónica - Electrónica Digital – Parte 1 (CUR5001S)

Curso de Electrónica Digital – Parte 2 - El Álgebra de Boole (CUR5002S)

Curso de Electrónica - Electrónica Digital - Parte 6 - Los Elementos Biestables (CUR5006S)

Curso de Electrónica - Electrónica Digital - Parte 9 - Contadores Digitales (CUR6002S)

Curso de Electrónica - Electrónica Digital - Parte 13 - Memorias, ADCs y DACs (CUR6006S)