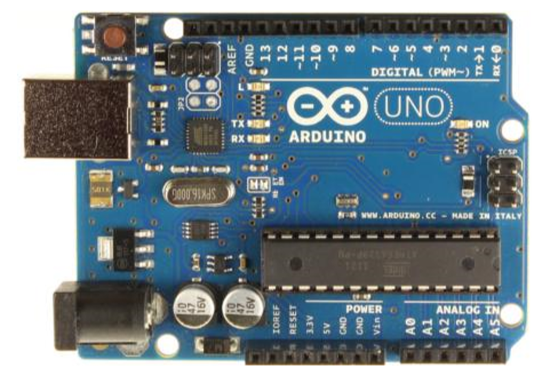

En los últimos años, la plataforma de desarrollo de Arduino ha crecido notablemente. Esto se debe a su fácil manejo, contribuciones de hardware y software e interés de empresas como Intel, Microsoft, Texas Instruments, etc., en adaptar sus productos a esta plataforma. Una de las tarjetas más usadas es la Arduino Uno, cuyo microcontrolador núcleo es el atmega328p. En este articulo conoceremos sus capacidades internas y arquitectura del microcontrolador, de gran utilidad a la hora de diseñar sistemas electrónicos.

La Figura 1 muestra la placa de Arduino Uno, cuyo hardware es abierto ( open ). Esto permite que muchas empresas de electrónica estén adaptando sus productos a esta plataforma. Por ejemplo, la Intel ha desarrollado placas siguiendo al Arduino Uno y usando algunos de sus procesadores. La Texas Instruments ha desarrollado placas siguiendo a Arduino Uno y usando algunos de sus microcontroladores. La IDE de desarrollo de Visual Studio de Microsoft, permite que por medio de un paquete de instalación, se pueda editar código para Arduino. Así, muchas empresas siguen el prototipo de Arduino. De ahí la importancia de conocer este sistema y su procesador núcleo, el ATmega328P. Este articulo muestra las principales características de este microcontrolador.

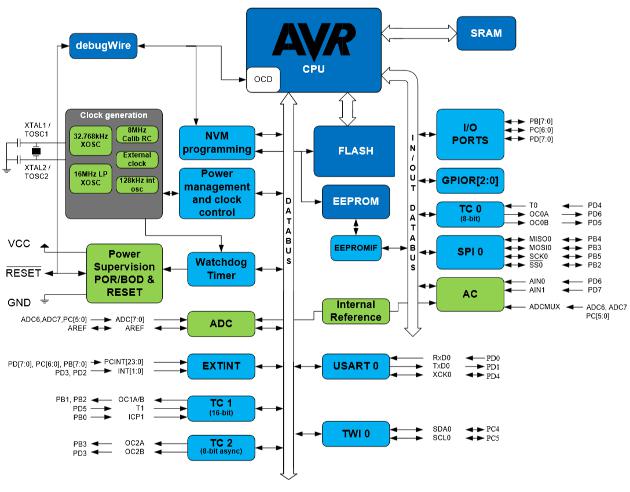

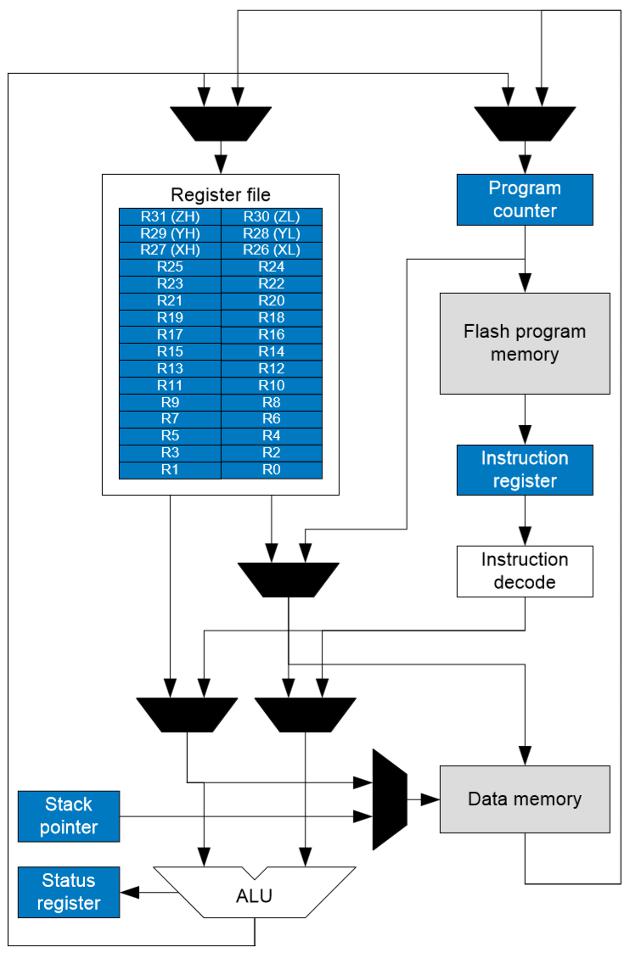

El ATmega328P es un microcontrolador de arquitectura RISC avanzado AVR de Atmel, de alto desempeño, bajo consumo y optimizado para compiladores C. La Figura 2 muestra el diagrama en bloques del microcontrolador. Entre sus principales características podemos encontrar:

- 131 Instrucciones potentes, la mayoría ejecutada en un solo ciclo de reloj.

- Un banco de 32x8 registros de propósito general.

- Hasta 20 MIPS (Millones de instrucciones por segundo) a 20 MHz.

- Un multiplicador hardware on-chip de 2 ciclos.

- Memoria de programa FLASH de 32 KBytes, programable dentro del sistema.

- Memoria SRAM interna de 2 KBytes.

- Memoria EEPROM de 1 KByte.

- 2 Timers/Contadores de 8 bits.

- 1 Timer/Contador de 16 bits.

- 6 Canales PWM.

- 6 Canales analógicos para el ADC.

- 1 Puerto serial USART.

- 1 Interface serial SPI.

- 1 Interface serial 2-Wire, compatible con I2C.

- 1 Timer watchdog.

- 1 Un comparador analógico on-chip.

- Interrupciones.

- Varios modos de bajo consumo.

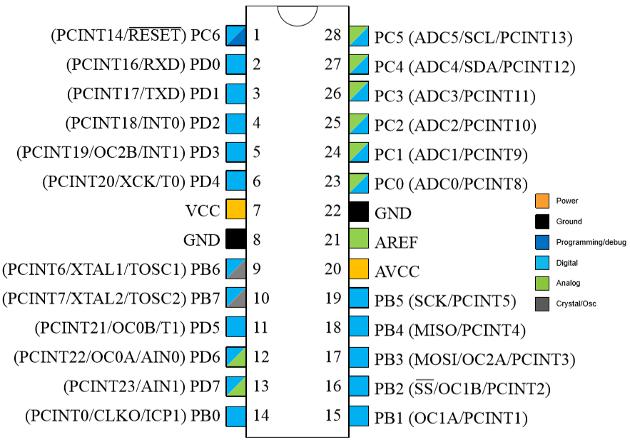

PINOS DEL MICROCONTROLADOR ATmega328P.

En la Figura 3 podemos observar los puertos, y pinos de voltaje. En total hay 23 entradas/salidas programables, para propósito general (GPIO). Estos pinos también pueden ser programados para funciones alternas, como comunicación serial, ADC, I2C, etc. Los siguientes son los puertos y pinos principales del microcontrolador:

VCC : Voltaje Digital.

GND : Tierra.

PORTB : Es un puerto bidireccional de 8 bits, con resistencias pull-up internas, seleccionables para cada pin. Las funciones alterna para los pinos del PORTB son:

- XTAL

- SPI

- Comparadores de salida (Output Comapare) para los Timers.

PORTC : Es un puerto bidireccional de 7 bits, con resistores pull-up internas, seleccionables para cada pin. Las funciones alterna para los pinos del PORTC son:

- Entradas analógicas (ADC)

- I2C.

PORTD : Es un puerto bidireccional de 8 bits, con resistencias pull-up internas, seleccionables para cada pin. Las funciones alterna para los pinos del PORTD son:

- Puerto serial USART.

- Interrupciones externas INT0 y INT1.

- Comparadores de salida para los Timers.

AVcc : Es el pin de voltaje para el conversor análogo para digital (ADC).

AREF : Pin de referencia análoga para el ADC.

ARQUITECTURA INTERNA DEL MICROCONTROLADOR ATmega328P.

En la Figura 4 se puede ver el diagrama en bloques de la arquitectura del microcontrolador ATmega328P. Este microcontrolador usa una arquitectura Harvard, usando memorias y buses separados para programa y datos. La CPU usa un pipeline (pipelining) de un nivel, es decir que mientras está ejecutando una instrucción, la próxima instrucción está siendo buscada (pre-fetched) desde la memoria de programa. Gracias a esta técnica de pipeline y buses separados, el microcontrolador puede ejecutar las instrucciones en un solo ciclo de reloj.

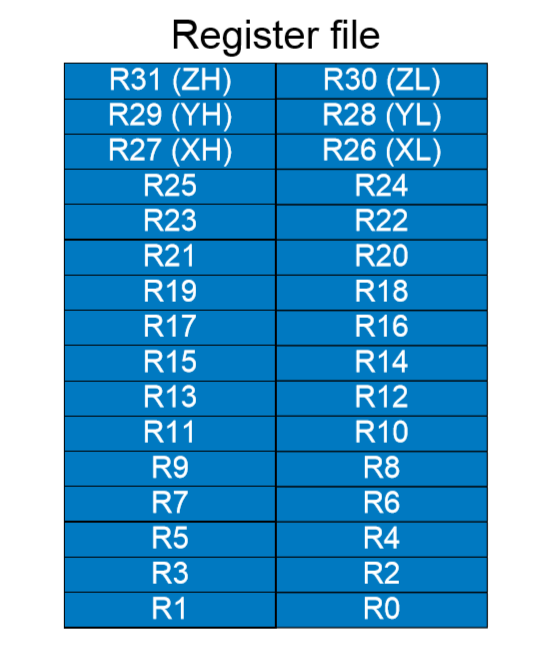

El microcontrolador también posee un banco (file) de registros de propósito general de 32 x 8 bits, con tiempos de acceso de un solo ciclo de reloj. Esto permite que las instrucciones aritméticas y lógicas (ALU), se puedan realizar en un solo ciclo de reloj. En la Figura 5 se puede observar el banco de registros. Hay 6 registros que se pueden usar como 3 registros de direccionamiento indirecto a la memoria de programa, habilitando eficiente cálculos de direcciones en la memoria de programa, muy utilizados en los programas C. Estos registros son llamados X, Y, Z y usan los registros 26 al 31.

MEMORIAS DEL MICROCONTROLADOR ATmega328P.

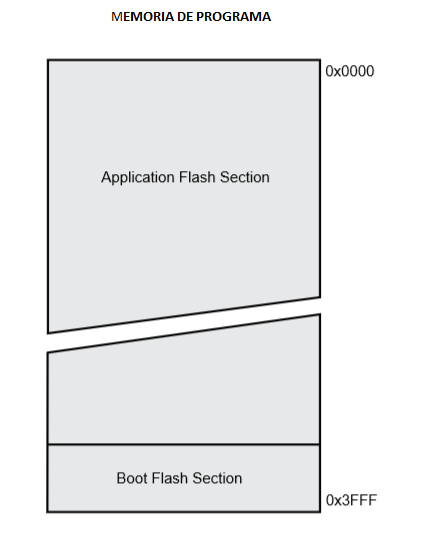

El microcontrolador ATmega328P tiene una memoria Flash 32 Kbytes reprogramable en el propio sistema o circuito, para el almacenamiento del programa. Como todas las instrucciones AVR son de 16 o 32 bits, la memoria Flash es organiza en 16K x 16. Para la seguridad del software, la memoria Flash de programa es divida en 2 espacios:

- La sección de inicialización de carga (Boot Loader).

- La sección de programa de la aplicación.

El contador de programa ( PC ) es de 14 bits, así puede direccionar los 16K de localizaciones de la memoria de programa. La Figura 6 muestra el mapa de direcciones para la memoria Flash.

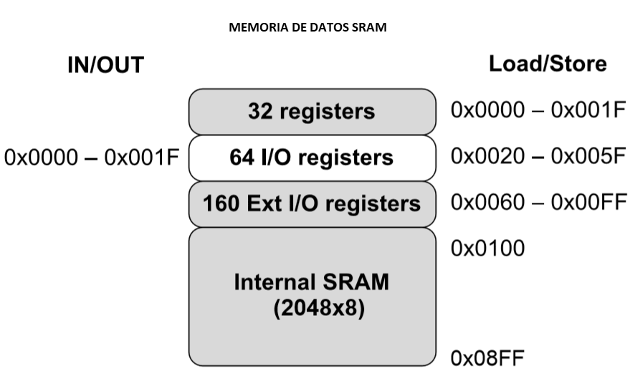

La memoria SRAM ( Static RAM ) es formada por 2303 localizaciones de memoria. En la parte más baja están: el banco ( file ) de registros de propósito general, luego la memoria de entradas/salidas, luego, la memoria de entradas/salidas extendidas y finalmente SRAM de datos. El banco de registros es de 32 bytes, la memoria de entrada/salida es de 64 bytes, la memoria de entrada/salida extendida es de 160 bytes y la SRAM de datos es de 2048 bytes. La Figura 7 muestra el mapa de memoria para la SRAM. Esta memoria puede ser direccionada de 5 formas diferentes:

- Direccionamiento directo.

- Direccionamiento indirecto con desplazamiento.

- Direccionamiento indirecto.

- Direccionamiento indirecto con pre-decremento.

- Direccionamiento indirecto con post-incremento.

Los 32 registros de propósito general, los 64 registros de entrada/salida, los 160 registros de entrada/salida extendidos y SRAM interna de 2K, son todos accesibles a través de estos modos de direccionamiento.

El microcontrolador tiene una memoria EEPROM de 1 KBytes. Ella está organizada como un espacio de memoria separado, la cual puede ser leída o escrita. La EEPROM permite 100.000 ciclos de escritura/borrado.

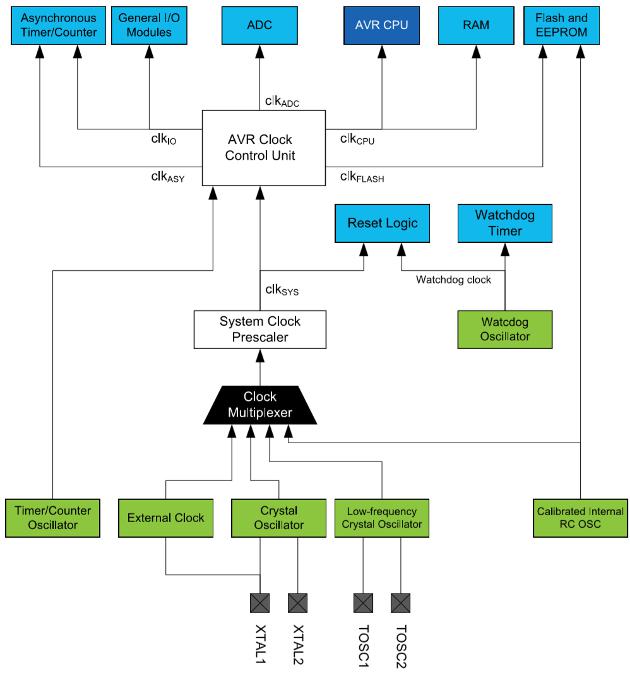

RELOJES DEL SYSTEMA ( CLOCKS ).

La Figura 8 ilustra los relojes ( clocks ) del microcontrolador y su distribución. No es necesario que todos los relojes estén activos al tiempo. Para reducir consumo, los módulos de reloj que no están siendo usados, pueden ser parados ( halted ) usando modos de bajo consumo diferentes.

El reloj de la CPU es llevado a partes del microcontrolador, concernientes al núcleo ( core ). Ejemplo de estas partes son: Los 32 registros de propósito general, memoria de datos, etc. El reloj de entradas/salidas es usado por módulos como los timers/contadores, SPI, USART, Interrupciones externas, etc.

Las fuentes de reloj para el microcontrolador pueden ser seleccionadas desde un cristal de baja o alta frecuencia externo, una señal digital de reloj externa, o un oscilador interno.

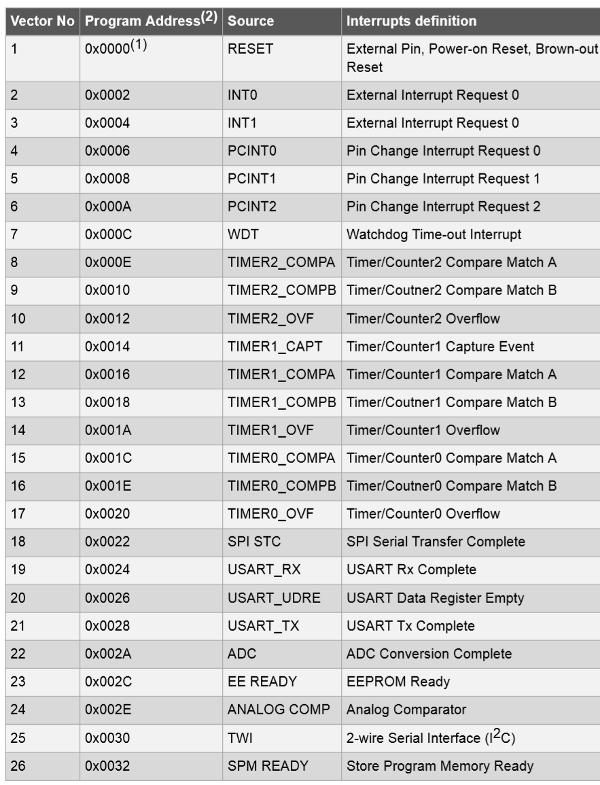

INTERRUPCIONES EN EL ATmega328P.

Interrupciones es el mecanismo de hardware por el cual el microcontrolador se entera que hay un evento urgente que atender. Para esto el microcontrolador deja el programa principal y atiende la interrupción, que es una rutina de código para atender a un evento en especial. Por ejemplo, si hubo un cambio de estado en un pin, o si llego un byte de dato en el puerto serie, o si se desbordo algún timer, o si se terminó la conversión en el ADC, etc., todos estos son casos típicos o comunes de interrupción que se pueden habilitar en microcontrolador. Las interrupciones externas se disparan por los pinos INT0 o INT1 y los pinos PCINT. Podemos notar, que mismo que estos pinos sean configurados como salida, la interrupción será disparada. Esto es muy útil a la hora de generar interrupciones por software.

Las interrupciones externas pueden ser disparadas por flanco de subida, o flanco de bajada o nivel bajo. Esta configuración se puede hacer en el registro de control de interrupciones externas ( EICRA ). La Figura 9 muestra la tabla de vectores de interrupción que el microcontrolador puede atender. Normalmente, es necesario habilitar la interrupción con algún bit, en algún registro de control. Para notificar que se ha producido un evento de interrupción, un bit (flag) se pone a '1'. Cuando la interrupción es atendida, este bit automáticamente es limpiado ( clear ) por hardware.

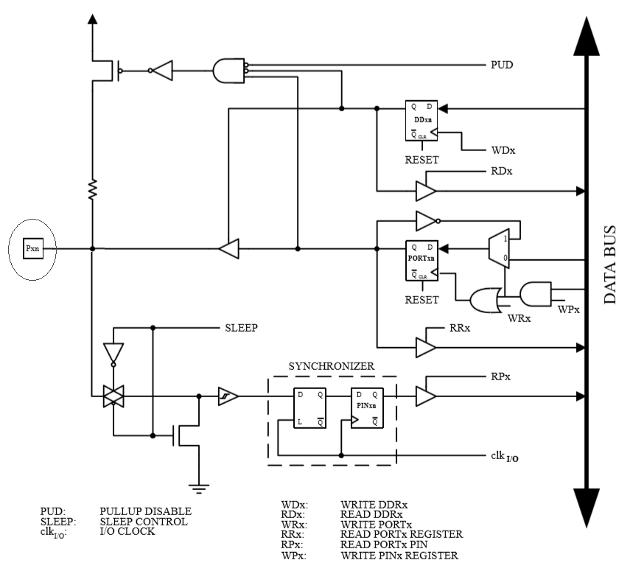

PUERTOS DE ENTRADA/SALIDA.

Todos los puertos tienen la funcionalidad de lectura-modificación-escritura cuando usados como pinos de entrada/salida. Esto significa que puede cambiar el valor de un bit sin modificar los otros, con las instrucciones Set Bit (SBI) y Clear Bit (CBI). La Figura 10 muestra la descripción funcional de un pin de entrada/salida del microcontrolador.

Cada pin de un puerto consiste de 3 bits. El DDxn en el registro DDRx selecciona la dirección de este pin. Si DDxn es escrito a '1', el correspondiente pin será configurado como salida. Si DDxn es escrito a '0', el correspondiente pin será configurado como entrada.

Para escribir datos en el puerto se usa el registro PORTx. Si PORTnx es escrito a '1', cuando el pin es configurado como salida, el pin del puerto es colocado a nivel alto. Si PORTnx es escrito a '0', cuando el pin es configurado como salida, el pin del puerto es colocado a nivel bajo.

Si PORTnx es escrito a '1', cuando el pin es configurado como entrada, la resistencia pull-up es activada. Para deshabilitar la resistencia pull-up, el PORTnx debe ser escrito a '0' o configurar el pin como salida.

Para leer el pin del puerto se usa el registro PINnx.

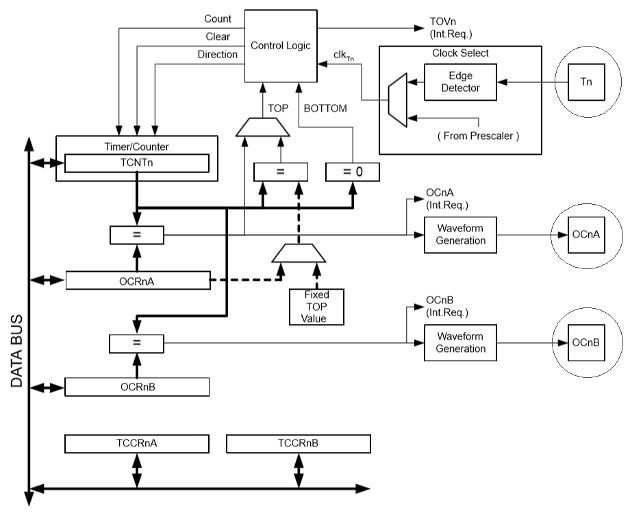

TC0 - TIMER/CONTADOR DE 8 BITS CON PWM.

El Timer/Contador es un módulo para temporizaciones y contaje de 8 bits de propósito general, con 2 unidades comparadoras de salida y soporte a PWM. Así, este módulo permite temporizar con precisión ejecución de programas y generación de ondas.

Entre las principales características del TC0, se encuentran:

- Tiene 2 unidades independientes con comparadores de salida.

- Registros en los comparadores de salida con 2 búfer.

- Clear en timer cuando iguala la comparación (Auto load).

- PWM (Pulse Width Modulador).

- Periodo PWM variable.

- Generador de frecuencia.

La Figura 11 muestra el diagrama en bloques de Timer/Contador 0. La unidad comparadora de salida, continuamente esta verificando si el registro TCNT0 es igual a los registros OCR0A y OCR0B. Si TCNT0 es igual a OCR0A o OCR0B, el comparador señala una igualdad, colocando el flag OCF0A o OCF0B. Si la correspondiente interrupción esta habilitada, el flag generara una interrupción de comparación de salida. El flag es automáticamente limpiado cuando la interrupción es ejecutada.

El timer/contador tiene varios modos de operación. El Modo Normal es el más simple. En este modo la dirección del contador es siempre hacia arriba (incremento). Cuando el contador alcance el valor programado, coloca a '1' el flag TOV1 de sobre flujo (overflow) y si habilitado, puede generar una interrupción. Este flag es automáticamente limpiado cuando la interrupción es ejecutada.

El timer 0 y el timer 2 son de 8 bits y sus características son muy similares. Ya el timer 1 es de 16 bits y tiene la característica de captura en una de sus entradas. Esto es muy útil para medir el ancho de pulsos provenientes de algún circuito exterior y así medir distancias o frecuencias.

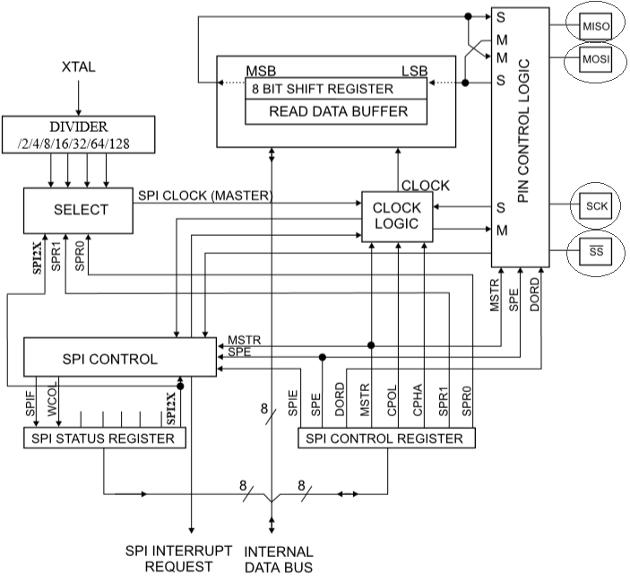

SPI - INTERFACE SERIAL DE PERIFERICOS.

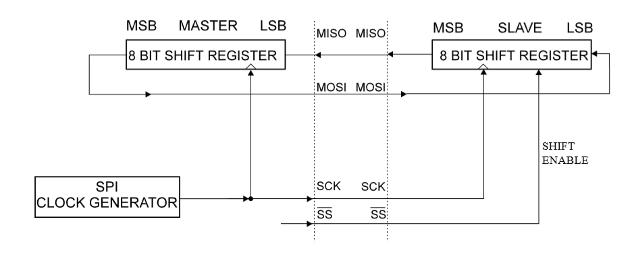

La Interface Serial de Periféricos (SPI) permite transferencia de datos síncronas de alta velocidad, entre el microcontrolador y unidades periféricas. En la Figura 12 podemos ver el diagrama de bloques de la SPI. La interconexión entre el Maestro y el esclavo es mostrada en la Figura 13. El sistema consiste de 2 registros de desplazamiento y un generador de reloj (clock) maestro. El maestro inicializa la comunicación cuando lleva a nivel bajo '0' el pin SS (Slave Selection) del esclavo, con el cual desea comunicarse. Maestro y esclavo preparan sus datos a ser enviados en sus respectivos registros de desplazamiento y el maestro genera los pulsos de clock requeridos en el pin SCK para el intercambio de datos.

El dato es desplazado de Maestro a Esclavo sobre la línea MOSI (Master Out - Slave In) y desde Esclavo a Maestro en la línea MISO (Master In - Slave Out). Después de cada paquete de datos transferido, el Maestro sincroniza el esclavo, llevando a alto '1' lógico el pin SS (Slave Selection).

El periférico SPI es de un solo buffer en el sentido de transmisión y con doble buffer en el sentido de recepción. Esto significa que bytes a ser transmitidos, no pueden ser escritos al registro de datos del SPI, antes que el ciclo de desplazamiento entero este completo. Cuando recibiendo datos, un carácter recibido debe ser leído del registro de datos SPI, antes que el próximo dato haya sido completamente desplazado adentro.

Las principales características de la SPI son:

- Full Duplex, transferencias de datos síncronas con 3 líneas.

- Operaciones maestras o esclavas.

- Transferencia de datos LSB primero o MSB primero.

- Generación de interrupción al fin de la transmisión.

- Protección para colisión en la escritura.

- Modo maestro de doble velocidad CK/2.

COMUNICACION SERIAL - USART (Universal Synchronous Asynchronous Receiver Transceiver)

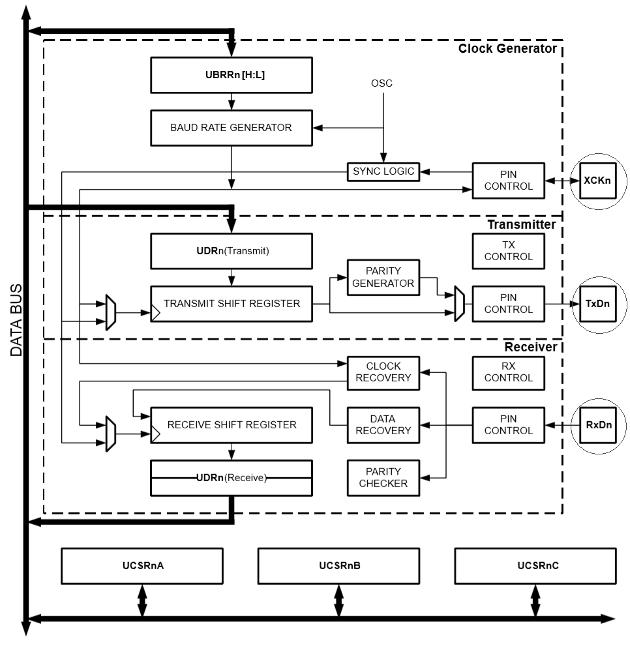

La USART es un periférico de comunicación serial altamente flexible. La Figura 14 muestra el diagrama en bloques de la USART de microcontrolador. En la parte superior, del diagrama de bloques, se encuentra el generador de reloj (clock), en el medio está el transmisor y en la parte baja está el receptor. Estos bloques son separados por líneas punteadas o descontinúas en el diagrama en bloques. Los registros de control son compartidos por todos los bloques.

La generación de pulsos consiste de: lógica de sincronización para entradas de reloj externa, usadas para operaciones con esclavos síncronos y para generar la velocidad de transmisión (baudios). El pin XCKn es usado solo por modos de transferencia síncronos.

El transmisor consiste de: un único búfer de transmisión, registro de desplazamiento serial, un generador de paridad y una lógica de control para manejar diferentes formatos de datos seriales (frames). El búfer de escritura permite transferencia continua de datos, sin cualquier retardo entre frames.

El receptor es la parte más compleja del periférico USART, debido a su clock y unidad de recuperación de datos. La unidad de recuperación es usada para la recepción asíncrona de datos. Además de la unidad de recuperación, el receptor también posee un verificador de paridad, lógica de control, un registro de desplazamiento y un búfer de recepción de 2 niveles (UDRn). El receptor soporta el mismo formato de frames como el transmisor y puede detectar errores de datos (frames), sobre flujo y errores de paridad.

Entre las principales características de la USART podemos encontrar:

- Operaciones full duplex (independiente registros para transmisión y recepción)

- Operaciones asíncronas y síncronas.

- Operaciones síncronas para comunicaciones Maestro Esclavo.

- Generador de baudios de alta resolución.

- Soporta frames de datos seriales de 5, 6, 7, 8 y 9 bits y 1 o 2 bits de parada (stop).

- Generador de paridad par o impar y verificación de paridad soportada por hardware.

- Detección de sobre flujo de datos.

- Detección de error en los frames de datos.

- Incluye filtros de ruido.

- Modo de comunicación multi-procesador.

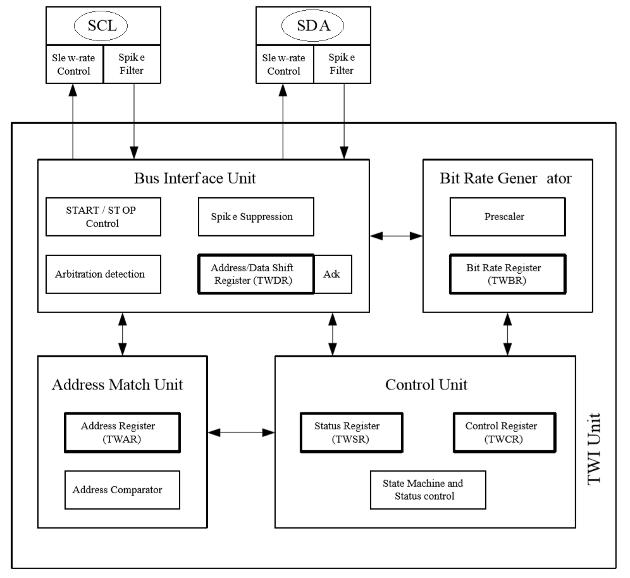

TWI - INTERFACE SERIAL DE 2 HILOS.

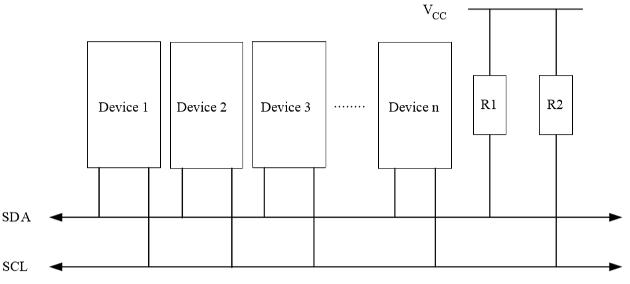

La Figura 15 muestra el protocolo TWI. El protocolo de la TWI (Two-Wire Serial Interface) permite interconectar hasta 128 diferentes dispositivos, usando solamente un bus bidireccional de 2 líneas: SDA para datos y SCL para el clock. El único hardware externo necesario para implementar el bus, es una única resistencia para cada línea del bus TWI. Todos los dispositivos conectados al bus tienen individual dirección.

Cada bit de dato transferido sobre el bus, es acompañado de un pulso sobre la línea de clock. La única excepción a esta regla, es para generar las condiciones de inicio (START) y de parada (STOP). El Maestro inicia y termina una transmisión de datos. La transmisión es iniciada cuando el maestro saca una condición de START sobre el bus y es terminada cuando el maestro saca una condición de STOP. Entre una condición de START y STOP, el bus se considera ocupado y ningún otro maestro debe intentar controlar el bus.

Todos los paquetes de direcciones transmitidos sobre el bus TWI, tienen un ancho de 9 bit, consistiendo de 7 bits para la dirección del esclavo, 1 bit de control para lectura/escritura y 1 bit de reconocimiento (acknowledge). Si el bit de lectura/escrita es colocado a '1' lógico, una operación de lectura seria ejecutada, si el bit es colocado a '0' lógico, una operación de escritura seria entonces ejecutada. Cuando un dispositivo esclavo reconoce que el esta siendo direccionado, el debe reconocer (ACK), llevando la línea SDA abajo (low) en el noveno ciclo de SCK. Entonces el maestro puede transmitir una condición de STOP.

Todos los paquetes de datos tienen un ancho de 9 bits, consintiendo de 8 bits para el dato y un bit de reconocimiento (ACK). Durante la transferencia de datos el maestro genera el clock y las condiciones de START y STOP, mientras que el receptor es responsable por el reconocimiento (ACK).

Una transmisión básicamente consiste de una condición de START, la dirección del esclavo y si es lectura o escritura, uno o más paquetes de datos y una condición de STOP.

La Figura 16 muestra el diagrama en bloques del periférico TWI. Entre las principales características del periférico TWI, podemos encontrar:

- Poderosa y flexible interface de comunicación usando solo 2 líneas.

- Soporta operaciones Maestras y Esclavas.

- El microcontrolador puede ser configurado como maestro o esclavo.

- Espacio de direcciones de 7 bits, permite hasta 128 dispositivos diferentes.

- Soporte para gerenciar varios Maestros.

- Velocidades de transferencia de 400 KHz.

- Circuitos supresores de ruido.

- Compatible con el protocolo I2C de Phillips.

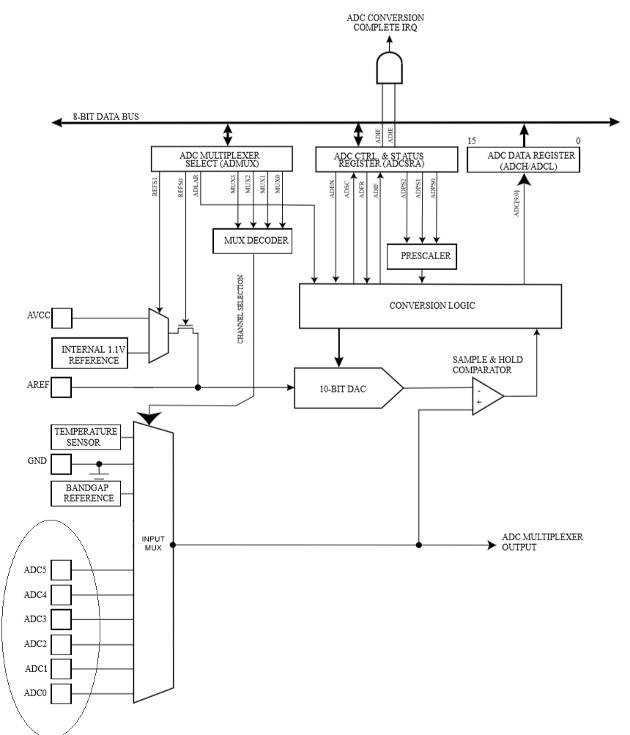

ADC - CONVERSOR ANALOGO PARA DIGITAL.

El microcontrolador posee un conversor análogo para digital de aproximación sucesiva de 10 bits. El ADC está conectado a un multiplexor analógico de 6 canales, permitiendo hacer entradas de voltaje, construidas en los pinos del puerto C (PORTC). El ADC contiene un circuito de muestreo y fijación (Sample and Hold) asegurando que la entrada al ADC es mantenida en un nivel constante durante la conversión. La Figura 17 muestra el diagrama en bloques del ADC. El ADC tiene un pin de alimentación de voltaje separado llamado AVcc y no debe ser diferente de más o menos 0.3 Voltios de Vcc.

El ADC convierte una entrada de voltaje analógico para un valor digital de 10 bits a través de aproximaciones sucesivas. El valor mínimo es representado por GND y el valor máximo representa el voltaje sobre el pin AREF. Opcionalmente, AVcc o un voltaje de referencia interno de 1.1 Voltios, pueden ser conectados al pin AREF. El voltaje de referencia interno debe ser decuplado por un capacitor externo en el pin AREF para mejorar la inmunidad al ruido.

El canal de entrada analógico es seleccionado, escribiendo a los bits MUX en el Registro de Selección del Multiplexor ( ADMUX.MUX[0:3] ). Cualquiera de las entradas analógicas, como también GND y un voltaje de referencia fijo, pueden ser seleccionados como entrada al ADC. El ADC genera un resultado de 10 bits, el cual es representado en los registros de dato del ADC ( ADCH y ADCL ). Por defecto el resultado es ajustado a la derecha, mas puede ser opcionalmente representado a la izquierda, colocando a '1' el bit de ajuste a la izquierda de ADC ( ADMUX.ADLAR ). El ADC tiene su propia interrupción, el cual puede generarse cuando una conversión es completada.

Para inicializar una conversión se debe escribir a '0' el bit de reducción de consumo en el Registro de Reducción de Consumo ( PRR.PRADC ) y escribir a '1' el bit de inicio de conversión ADC ubicado en el Registro A de control y estado del ADC ( ADCSRA.ADSC ). El bit ADSC permanecerá alto, tanto tiempo como la conversión este en progreso y será limpiado por el hardware, cuando la conversión este completa. Por defecto, el circuito de aproximación sucesiva requiere una entrada de frecuencia de reloj entre 50 KHz y 200 KHz para conseguir resolución máxima.

Las principales características del ADC son:

- Resolución de 10 bits.

- Tiempos de conversión entre 13 y 260 micro segundos.

- 6 canales de entrada multiplexados.

- Canal de entrada con sensor de temperatura.

- Opcional ajuste de lectura hacia la izquierda.

- Rango de voltaje de 0 hasta Vcc.

- Voltaje de referencia de 1.1 Voltios para el ADC.

- Modo de conversión único o libre.

- Interrupción cuando la conversión sea completada.

- Cancelación de ruido en modo de bajo consumo ( SLEEP ).

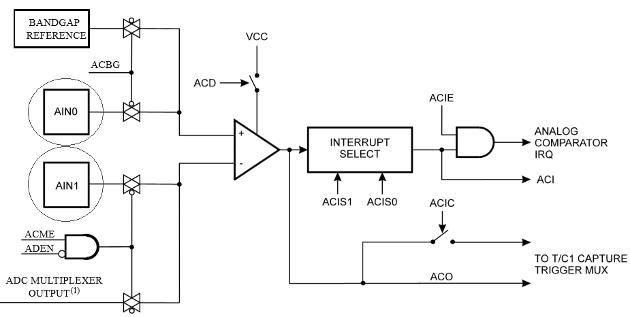

AC - COMPARADOR ANALOGICO.

El comparador analógico compara los valores de entrada sobre el pin positivo AIN0 y pin negativo AIN1. Cuando el voltaje sobre el pin positivo AIN0 es más alto que el voltaje sobre el pin negativo AIN0, la salida el comparador analógico ( ACO ) es colocado a '1' . Esta salida puede ser usada para disparar la función de captura del timer/contador 1. Además, el comparador analógico puede disparar una interrupción separada. El usuario puede escoger el disparo de la interrupción de salida del comparador cuando el bit ACO suba, baje o cambie su estado ( toggle ). La Figura 18 muestra el diagrama de bloques de comparador analógico.